# APPLICATION NOTE | AN:038

# HV ChiP<sup>™</sup> BCM<sup>®</sup> Reverse Start Up Circuit

David Bourner

| Contents                                                                  | Page         |

|---------------------------------------------------------------------------|--------------|

| Summary                                                                   | 1            |

| Scope and Arrangement of<br>Material                                      | - 1          |

| Introduction                                                              | 1            |

| Overview of Reverse Primer<br>Circuit Action                              | 2            |

| Primer Circuit Details                                                    | 3            |

| HUB (Hold-Up Capacitor) an<br>HSW (HUB Switch)                            |              |

| Command and Control Circ                                                  | <u>uit 8</u> |

| Auxiliary DC Regulator                                                    | 8            |

| Summary                                                                   | 9            |

| Disclaimer                                                                | 9            |

| References                                                                | 9            |

| Appendix                                                                  | 10           |

| Tables                                                                    | 10           |

| <u>Oscillograms</u>                                                       | 10           |

| Partitioned BOM for BCM<br>Reverse Primer Circuit                         | 11           |

| <u>Flyback Converter Block</u><br>(Pulse Generator + Flyba<br>Powertrain) | ack_         |

| HUB (Hold-Up Capacito<br>and HSW (HUB Switch)                             |              |

| Command and Control                                                       |              |

ge Summary

An economical, robust circuit for reverse starting Vicor HV (high-voltage) ChiP (Converter Housed-in-Package) BCM (Bus Converter Module) engines with analog mode control is described. The way the circuit works is explained.

## Scope and Arrangement of Material

In the conventional mode, a DC source voltage is applied to the primary or high-voltage side of the BCM with its secondary port loaded. The BCM primary and secondary power ports are isolated. The BCM's controller is set on the primary side of the BCM. A BCM can be operated in another way, which is called reverse mode [ref 6]. In this configuration, source and load are swapped with each other: the source is set across the secondary port and load set across the primary port. To process power in this way, the BCM's controller has to be "primed" first; once this is done, the primary-port-based load will receive power through the BCM with power sourced from the secondary port.

This app note presents a discrete component circuit for automatic start up of analog-controlled, HV ChiP-formatted BCMs in reverse mode. The advent of routine BCM reverse start up opens up a wide field of applications. Examples of the use of a reverse or bidirectional BCM are seen in battery and super capacitor conditioning circuits, EV automotive power harvesting, and in HV DC tether voltage generation for UAV and AUVs [refs 4-6]. This note will pave the way to resolve issues associated with the start up of complex systems and the sequencing of power flow operations. (Dealing with arrays of BCMs is beyond the scope of this application note. Vicor Applications Engineering should be contacted about these unique applications.)

Much of the detail, associated with the BOM (bill of materials), waveform oscillograms of the operation of the primer and the like are provided in the appendix.

### Introduction

12

BCM and VTM<sup>™</sup> power components are members of the Sine Amplitude Converter (SAC<sup>™</sup>) family. The internal controller subsystems of all SACs developed and manufactured to date are referenced to the primary side of their isolation barriers. In order to allow power flow through a SAC, irrespective of its direction, it is necessary to first activate the controller by feeding it a primary-referenced supply voltage.

HV ChiP BCMs that have no primary HV (high-voltage) energy source available can be started or primed with the low-cost circuit described herein. The energy needed for start up is transferred from a secondary LV (low-voltage) DC source as a charge packet stream. This source is anticipated to be part of the mainstream application of the BCM: it is assumed to be permanently connected to the secondary side of the BCM. The trickle of current from the LV source is directed across the BCM's isolation barrier to a HUB (hold-up capacitor). Once charged, the HUB is connected for a short time to the primary power port of the BCM. After start up of the BCM and reverse mode confirmation, the primer circuit goes into a low-power state.

The primer system comprises a pulse generator, a low-power flyback converter, hold-up capacitor (HUB), unidirectional switch and command and control logic. The flyback powertrain has no linear feedback control loop installed. The powertrain is either ON or OFF, depending on the voltage of the hold-up capacitor and its relation to the BCM's input voltage turn-on threshold. A comparator and logic gating automatically sequences the circuit's various phases of operation.

Three variations can be made to the reverse BCM primer. The first adaptation makes it possible to accommodate some BCM applications that already have external filtering elements installed across the input port of the BCM. The second adaptation allows the circuit to work with either low- or high-voltage secondary DC power sources. A third adaptation is available for adjusting the primer circuit's turn-on threshold.

Auxiliary Linear Regulator 12

Circuit

#### **Overview of Reverse Primer Circuit Action**

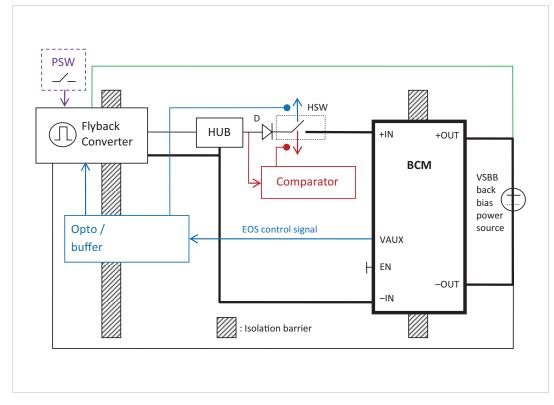

Figure 1 shows the reverse BCM<sup>®</sup> primer block diagram. The circuit elements in the BCM's secondary domain include a linear regulator, R-C pulse generator and flyback powertrain all included in the "Flyback Converter" block. This is followed by the HUB (hold-up capacitor) and switch HSW. The closure of this switch is not timed, but depends instead on the threshold set within the starter circuit for activating the BCM. In the specific case of HV BCMs, an opto-isolator drive is connected to the BCM's VAUX terminal. This signal will flag termination of the priming process, deactivating the pulse generator circuit drive and flyback powertrain.

There are predefined voltage ranges for the VSBB (Voltage Source, providing secondary Back-Bias) that must not be exceeded. Rate of change of the VSBB source must also be controlled so that it does not introduce resonances or unexpected transients within the BCM.

With a correctly pre-configured VSBB source in place across the BCM's secondary port, the priming sequence occurs on closure of switch PSW. A linear auxiliary regulator that develops an internal 8V<sub>DC</sub> rail is activated. This initiates pulse generation and the flyback converter starts switching. This powertrain delivers energy at high voltage for charging the HUB (hold-up capacitor) via a current-limiting resistor. Once the HUB voltage reaches a level that puts it well over VIN UVLO+ for the BCM (input undervoltage lockout threshold – see BCM data sheet), a comparator closes the one-way switch HSW between the HUB and current-limiting resistor across the inactive BCM's primary circuit. This connection is held closed to start up the BCM.

Switch HSW opens if the reflected secondary supply voltage is greater than that delivered to the BCM by the HUB during the priming process. This condition would be consistent with a fully activated BCM being back-fed with the secondary source VSBB set at the high end of the BCM's secondary operational voltage range.

Shortly after start up has been initiated, the BCM indicates that is has been successfully primed by setting its VAUX terminal 'HIGH'. The starter is then latched OFF after reverse mode confirmation. The auxiliary DC regulator is disabled and the internal DC rail drops from 8V to approximately 1.2V; the pulse generator goes into an inactive state. This puts the low-side power switch in cut-off mode (see Figure 4 for circuit detail).

## Figure 1 System block diagram for

BCM reverse starter

The reverse primer's automatic self-lockout from the BCM<sup>®</sup> power path avoids a situation where the start up circuit gets prematurely re-engaged. The BCM telegraphs secondary voltage fluctuations back to its primary port that are sometimes sufficient to disable its primary-referenced controller. To reset the primer, it is a simple matter to open the switch PSW and then re-close it after a short delay to reinitiate the priming sequence. The amount of time for the reset will be determined by the application circuit within which the BCM is embedded.

### **Primer Circuit Details**

The BCM's primary-to-secondary isolation rating is preserved in the presence of the reverse starter circuit through the careful selection of an appropriate coupled inductor used in the flyback powertrain. This is rated at  $3000V_{RMS}$  which is consistent with the isolation afforded by the HV ChiP<sup>TM</sup> BCM family of products. The flyback powertrain has power applied to its primary circuit via a linear regulator. It is important for the flyback primary supply voltage to be held close as possible to  $8V_{DC}$  during primer engagement.

Given the range of secondary voltages for HV ChiP-based BCM products (refer to Table 1), it is feasible to deploy a DC linear regulator which draws current from the VSBB source either with or without a power-limiting resistor. Note also that the different BCM secondary voltage ranges "map" to one of two different voltage reference limiting resistor values associated with those ranges.

| BCM Primary Voltage<br>BCM V <sub>PRI</sub> (V <sub>DC</sub> ) | BCM Secondary Voltage<br>BCM V <sub>SEC</sub> (V <sub>DC</sub> ) | Linear Regulator & VSBB V <sub>REF</sub><br>Option |

|----------------------------------------------------------------|------------------------------------------------------------------|----------------------------------------------------|

| 260 → 410                                                      | 32.5 → 51.3                                                      | UR                                                 |

| 260 → 410                                                      | 25.0 → 50.0                                                      | UR                                                 |

| 260 → 410                                                      | 16.3 → 25.6                                                      | STD                                                |

| 260 → 410                                                      | 8.1 → 12.8                                                       | STD                                                |

### Table 1

HV ChiP BCM input / output voltage ranges supported by the reverse primer circuit

This auxiliary linear regulator powers the circuits in the flyback converter block of Figure 1. The provision of this DC rail is subject to the customer's application. For instance, it is possible to deploy an auxiliary rail that is independent of the secondary back bias source VSBB, as the customer chooses. This regulator will only be active for a matter of a few seconds during priming. In its OFF state, it is expected that the power draw of the standard linear regulator applied in this note will be a few milliwatts.

The R-C clock oscillator internal to the flyback converter block generates a 100kHz square-wave for the low-side MOSFET power switch in the flyback converter. The oscillator is able to operate with DC bias set between 3.5V and  $16V_{DC}$ . With the 8V bias, the pulse train waveform's mark-time keeps the volt-second balance at an optimal level in the coupled inductor. The timing is also designed to ensure that the flyback converter operates in discontinuous conduction mode, allowing it to rapidly charge the hold-up capacitor. The time delay associated with the start up process will vary in accordance with the selected HUB capacitor's size (10 –  $100\mu$ F), its voltage coefficient, tolerance and temperature. The circuit uses a comparator for HUB switching, so it is not affected by these HUB variations. Thresholds in the comparator circuit are resistor-programmed, depending on the particular BCM in use.

To use Table 1, select a particular BCM and identify its input and output voltage ranges on its data sheet. Find the coincident condition in the table. This indicates whether the linear regulator will need to be adapted for either 'STD' or 'UR' – standard or upper range – VSBB source voltages.

The primer charges the HUB to a voltage consistent with the preset turn-on threshold. The comparator closes the HUB switch HSW and a pulse of charge, sufficient to turn on the BCM is transferred from the HUB.

The current delivered by the HUB is consistent with the highest no-load power draw of a BCM running in forward mode. Taking one example, a BCM rated to dissipate no more than 27W of no-load power, with activation level set to  $330V_{DC}$ , this current is determined to be slightly less than 82mA for a part such as the BCM6123TD1E13A3TOR. The current limit at  $330V_{DC}$  is consistent with the maximum continuous current handling capability of the high-voltage PMOS FET Q1 located in the HUB / HSW assembly (see Figure 5).

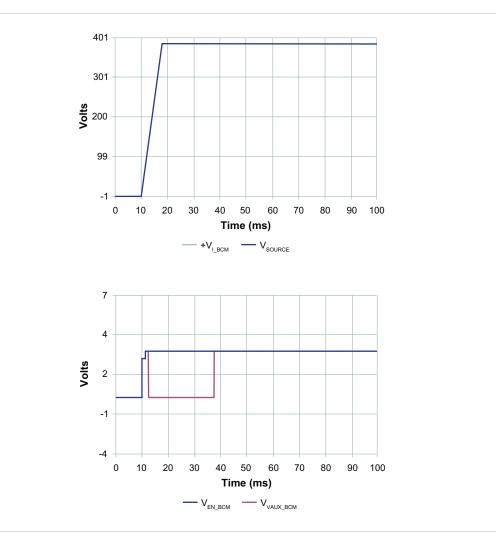

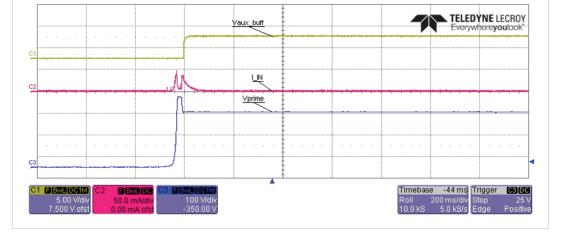

After the BCM's internal controller has been activated, it executes a series of housekeeping checks. Once the controller completes its checklist program, it signals that the BCM<sup>®</sup> is ready to process power by sending two pulses to the VAUX pin, as shown in Figure 2. The opto-isolator/buffer block reacts only to the second positive-going step transition of the VAUX signal, which follows the initial short pulse some 20 - 30 milliseconds later. The buffered EOS (end of start up) signal (shown in Figure 1) disengages the auxiliary regulator. The auxiliary regulator's output voltage drops from 8V to  $1.25V_{DC}$ . The output voltage of the flyback converter collapses to zero. A blocking diode, D, situated in the output lead of the converter, blocks backward current that would otherwise return to the HUB.

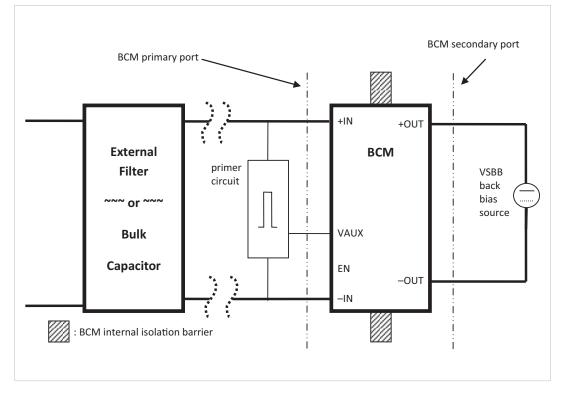

The choice of the HUB is contingent on the nature of input filtering network set between the load (or source) of the BCM on its primary port to be "hot-plugged" through the network. It is also a strong determinant in SAC<sup>TM</sup> applications for attaining successful start up (please consult Vicor Applications Engineering if other SACs need to be primed). In relation to external pre-installed EMI filtering, it has been found that a 100µF HUB may allow adequate charge delivery to the BCM – in spite of the sneak paths that parallel it. In the standard applications filter circuit that precedes the primary port of the BCM, bulk capacitance is not applied across the BCM's primary port, so a 10µF HUB is adequate. If the loading is heavy, then it will be necessary to "hot swap" the filter network and the downstream source/load combination in the primary circuit, once the BCM is fully operational. This is outlined in Figure 3.

The BOM is broken down in accordance with the different functions that were initially identified in the outline block diagram of Figure 1. The BOM for the reverse starter circuit is included in the Appendix.

#### Figure 2

Simulation of BCM showing V<sub>IN</sub> ramping in the top trace; the purple trace is the EOS signal which appears on the BCM's VAUX terminal as a "power good" flag

# Figure 3

Showing the reference plane across which the HUB is to be switched into the BCM<sup>®</sup> for start up

### **Flyback Converter Block**

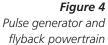

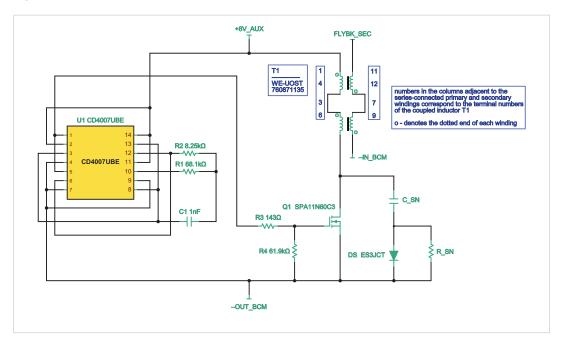

The flyback converter block comprises a pulse generator and the flyback powertrain. The pulse generator (shown on the left hand side of Figure 4) is based on an R-C oscillator that utilizes unbuffered inverters and MOS switches contained in the CD4007UBE [ref 2]. The flyback powertrain comprises a drive termination network, the main power switch, R-C-D snubber and  $3000V_{RMS}$  rated coupled inductor. Note that the snubber R-C component selections are impacted by parasitic inductance associated with the switching node of the primary-side circuit. To proceed with some tentative values, setting R\_SN to  $681\Omega$  and C\_SN to 390pF will provide the basis of compensating the flyback powertrain switching node. When laying out a PCB, minimizing the pad size of the power switching MOSFET's drain node will reduce parasitics. Although values are stated, it is advisable to make measurements with the initial components selected and adjust the snubber network values until there are no significant switching oscillations present on this critical node.

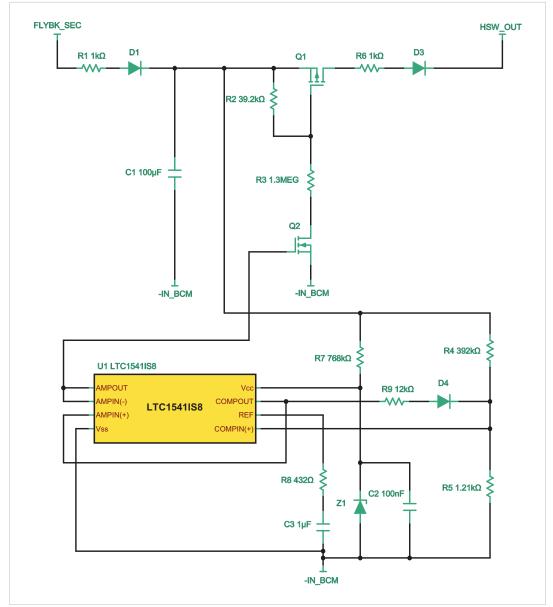

#### HUB (Hold-Up Capacitor) and HSW (HUB Switch)

The HUB (hold-up capacitor) and the HSW (HUB switch) schematic sections are shown in Figure 5. An electrolytic capacitor is set to one of two values, depending on the BCM<sup>®</sup> primary capacitance that needs to be 'swamped' by the HUB. Tracing from the FLYBK\_SEC (flyback secondary winding node) terminal on the left hand side of the schematic to the right, there is high-voltage blocking diode D1 and R1, a current-limiting resistor. This assures a current-limited start up of the flyback powertrain. If the external input filter or bulk capacitor electrolytic or ceramic capacitors present very low impedance in relation to the HUB, these will need to be temporarily disconnected in order to permit reliable reverse start up of the BCM.

To be clear, the starter circuit is not designed to bring up both the BCM and power elements connected ahead of its primary port. It is only capable of applying sufficient current at the correct voltage to the BCMs HV input power port alone, as shown in Figure 3. Customers with applications involving large amounts of capacitance placed at the BCM input port should consult Vicor Applications Engineering. The impedance of the inactive BCM reverse starter is very small to the extent that it should not affect the response of input filtering, particularly to CE (conducted emissions), once disabled after deployment. It has been found that in optimal CE suppression applications, that no bulk differential capacitor should be connected across the BCM input power port. Absence of external applied input capacitance prevents common-mode noise imbalance in such networks.

Moving to the right of the HUB, a PMOS high-side switch assembly is controlled by a comparator. The comparator senses the voltage build-up across the HUB as it charges. The comparator activates the HSW once its turn-on threshold is reached.

The threshold is easily calculated with the following equation

### **Equation 1**

$$V_{threshold} = \left(\frac{R4 + R5}{R5}\right) \bullet V_{rej}$$

In the example schematic of Figure 5, V<sub>threshold</sub> is 393V, set with R4 = 392k $\Omega$  and R5 = 1.2k $\Omega$ . In the LTC1541, the reference voltage V<sub>REF</sub> = 1.2V.

Hysteresis is afforded by the addition of two components, R9 and D4 as shown in Figure 5. It can be shown that the HSW will maintain a current path between the HUB and the BCM<sup>®</sup> as the HUB discharges from 393V down to approximately 272V. In the meantime the BCM will be expected to have been primed and that it will signal EOS before the HUB voltage drops to its cutoff value.

# Figure 5

HUB (designated as C1) and HSW assembly for UR option as displayed in Table 1.

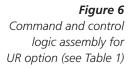

# **Command and Control Circuit**

The Command and Control circuit includes the EOS (end of start up) control signaling and the opto-isolator elements as shown in the block diagram of Figure 1. The circuitry is shown in Figure 6.

The start-up process starts with the closure of a manual SPST switch PSW. On closure of PSW, the start up regulator is enabled via the pulling down of the SHDN signal line. The BCM will then be subject to start-up processes. When the BCM<sup>®</sup> presents a 3V positive-logic signal pulse and step, each of these gets transmitted through the opto-isolator and filtered with the R3-C1 network, leaving only the positive step signal. The processed step (EOS) signal that appears on the VAUX terminal, once the BCM is ready to process power, is buffered by U2. This circuit's action turns off the auxiliary DC regulator used to operate the flyback powertrain. PSW can be replaced with a transistor and controlled with user-provided external logic.

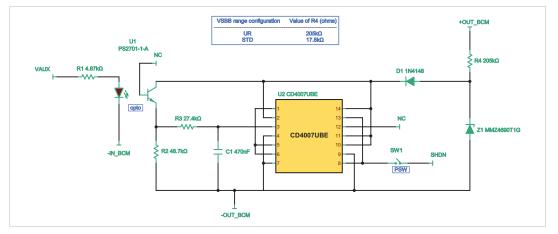

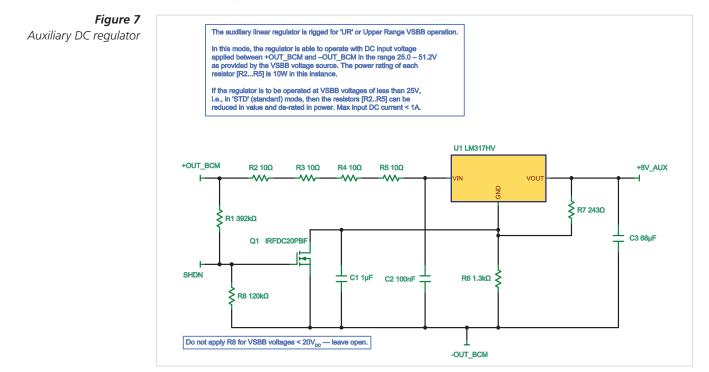

### **Auxiliary DC Regulator**

A DC-regulated low-voltage source has been contrived. It preserves the use of the same flyback powertrain with VSBB voltages of between 10.5 and 55V. Refer to Figure 7 for the schematic. This produces  $8V_{DC}$  at a maximum current of 500mA. The SHDN terminal is driven by the command and control circuit to turn off the auxiliary regulator after reverse priming has been accomplished. The LM317HV is thermally limited. With bias voltages in excess of  $25V_{DC}$  applied to it, it is necessary to insert power resistors ahead of the regulator's  $+V_{IN}$  terminal. These four power limiting resistors should not be incorporated into the start-up regulator if the applied voltage from the secondary bias source is less than  $25V_{DC}$ .

# VICOR

#### **Summary**

A reverse primer circuit, initially proposed for HV ChiP™ BCM<sup>®</sup> components with Analog Control, has been presented. It is adaptable to the needs of starting up other SAC<sup>™</sup> power components in the Vicor portfolio, such as VIC VTM<sup>™</sup>, with slight modifications. Other configurations may be available for this. Please contact Vicor Applications Engineering for further details.

#### **Disclaimer**

It should be noted that only reversible BCMs and VTMs have been formally qualified by Vicor for applications involving continuous reverse or bidirectional duties. Please note that Vicor outlines its Warranty Policy on each of its products' data sheets.

#### References

- 1. A Pressman, K. Billings, T. Morey, *Switching Power Supply Design*, 3rd edition McGraw Hill 2009 ISBN 978-0-07-148272-1

- COS/MOS Oscillator Frequency Calculator: <u>www.theremin.us</u> attributed to Arthur Harrison, based on theory outline in ICAN-6466, RCA 1970

- **3.** <u>http://www.vicorpower.com</u> Vicor website

- **4.** X. Lu, P. Yeaman, "A New High Efficiency Isolated Bi-Directional DC-DC Converter for DC-Bus and Battery-Bank Interface." *APEC* 2014

- **5.** G. Prophet, "Bidirectional DC/DC conversion enables efficient back-up power configurations." *EDN Europe* Apr. 29, 2014

- 6. D. Bourner, "Reverse Mode Application of Sine Amplitude Converters." Vicor White Paper http://powerblog.vicorpower.com/2016/06/white-paper-describes-reverse-mode-operation-sacs

# **Appendix**

# Oscillograms

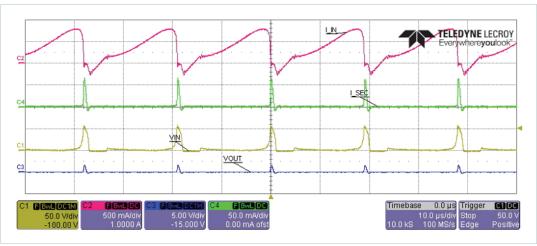

#### Figure A1 Flyback powertrain, 1.5ms after PSW engagement; primary and secondary inductor currents are shown along with input and output voltage waveforms

**Figure A2** Start up signaled with buffered VAUX EOS signal for BCM6123TD1E13A3TOR biased

with minimal VSBB potential.

**Note:** There are two current pulses in the red trace. The first one is associated with current delivery to the BCM<sup>®</sup> from the HUB to start the BCM up. The BCM input voltage peaks at it gets 330V set across its input power port. The BCM input comes up to this imposed level, and then settles. Prior to this test, the VSBB voltage was adjusted to lowest setting, which is 8.1V<sub>DC</sub>. The BCM reflects 260V onto the primary port, this voltage being at a level that permits another small pulse of current to be delivered by HUB which is still receiving charge from the flyback. At the instant that VAUX transitions for the second and final time, charge transfer from the primer to the BCM is terminated.

# Partitioned BOM for BCM Reverse Primer Circuit

| Designator | Description                                | Manufacturer      | Manufacturer<br>Part Number |  |

|------------|--------------------------------------------|-------------------|-----------------------------|--|

|            |                                            |                   |                             |  |

|            | Pulse Generator                            |                   |                             |  |

| U1         | IC CMOS DUAL COMP PR W INV 14-PIN          | TEXAS INSTRUMENTS | CD4007UBE                   |  |

| C1         | CAP C0G 1nF 5% 50V                         | -                 | -                           |  |

| R1         | RES 68.1kΩ 1%                              | -                 | -                           |  |

| R2         | RES 8.25kΩ 1%                              | -                 | -                           |  |

|            |                                            |                   |                             |  |

|            | Flyback Powertrain                         |                   |                             |  |

| Q1         | MOSFET N-CH 600V 11A TO220-3               | INFINEON          | SPA11N60C3XKSA1             |  |

| T1         | UNIV OFFLINE XFMR 1.25mH, 4kV              | WURTH ELECTRONIK  | 760871135                   |  |

| R3         | RES 143Ω 1%                                | -                 | -                           |  |

| R4         | RES 61.9kΩ 1%                              | -                 | -                           |  |

| R_SN       | RES 681 $\Omega$ 1% (initial suggestion)   | -                 | -                           |  |

| C_SN       | CAP X7R 390pF 10% 50V (initial suggestion) | -                 | -                           |  |

| DS         | DIODE GEN PURP 600V 3A SMC                 | ON SEMI           | ES3J                        |  |

# Flyback Converter Block (Pulse Generator + Flyback Powertrain)

## HUB (Hold-Up Capacitor) and HSW (HUB Switch)

| Designator | Description                       | Manufacturer     | Manufacturer<br>Part Number |

|------------|-----------------------------------|------------------|-----------------------------|

| U1         | IC µPWR OPAMP, COMP, REF 8-PIN SO | ANALOG DEVICES   | LTC1541IS8#PBF              |

| Q1         | MOSFET P-CH 500V 0.1A TO92-3      | MICROCHIP        | VP2450N3-G                  |

| Q2         | MOSFET N-CH 600V 320mA4-PIN DIP   | VISHAY SILICONIX | IRFDC20PBF                  |

| D1, D3     | DIODE 600V 3A SMC                 | ON SEMI          | ES3J                        |

| D4         | DIODE GEN PURP 100V 200mA DO35    | ON SEMI          | 1N414TA                     |

| Z1         | DIODE ZENER 5.6V 1% 50µA          | ON SEMI          | MMSZ4690T1G                 |

| C1         | CAP ALEL 100µF 10% 450V           | -                | -                           |

| C2         | CAP X7R 100nF 10% 50V             | -                | -                           |

| С3         | CAP FILM 1µF 10% 16V              | -                | -                           |

| R1, R6     | RES 1.0kΩ 1% 0.25W                | -                | -                           |

| R2         | RES 39.2kΩ 1%                     | -                | -                           |

| R3         | RES 1.3MΩ 1%                      | -                | -                           |

| R4         | RES 392kΩ 1%                      | -                | -                           |

| R5         | RES 1.21kΩ 1%                     | -                | -                           |

| R7         | RES 768kΩ 1%                      | -                | -                           |

| R8         | RES 432kΩ 1%                      | -                | -                           |

### **Command and Control Circuit**

| Designator | Description                                | Manufacturer      | Manufacturer<br>Part Number |

|------------|--------------------------------------------|-------------------|-----------------------------|

| U1         | OPTO-ISOLATOR 3.75kV TRANS 4-SMD           | CEL               | -                           |

| U2         | IC CMOS DUAL COMP PR W INV 14-PIN          | TEXAS INSTRUMENTS | -                           |

| D1         | DIODE GEN PURP 100V 200mA DO35             | ON SEMI           | 1N4148TA                    |

| Z1         | ZENER DIODE 5.6V 5% 50µA                   | ON SEMI           | MMSZ4690T1G                 |

| C1         | CAP X7R 470nF 16V                          | -                 | -                           |

| R1         | RES 4.87kΩ 1%                              | -                 | -                           |

| R2         | RES 48.7kΩ 1%                              | -                 | -                           |

| R3         | RES 27.4kΩ 1%                              | -                 | -                           |

| R4         | RES 205k $\Omega$ 1% (use for UR config)   | -                 | -                           |

|            | RES 17.8k $\Omega$ 1% (use for STD config) | -                 | -                           |

| SW1        | SPST SWITCH                                | -                 | -                           |

# Auxiliary DC Regulator

| Designator        | Description                                       | Manufacturer      | Manufacturer<br>Part Number |

|-------------------|---------------------------------------------------|-------------------|-----------------------------|

| U1                | IC REG LDO ADJ 1.5A TO220-3                       | TEXAS INSTRUMENTS | LM317HVT/NOPB               |

| Q1                | MOSFET N-CH 600V 320mA 4-PIN DIP                  | VISHAY SILICONIX  | IRFDC20PBF                  |

| C1                | CAP FILM 1µF 16V                                  | -                 | -                           |

| C2                | CAP X7R 1nF 100V                                  | -                 | -                           |

| С3                | CAP ALEL 68µF 63V                                 | -                 | -                           |

| R1                | RES 392kΩ 1%                                      | -                 | -                           |

| R2, R3,<br>R4, R5 | RES 10 $\Omega$ 2.5W 10% (use for UR config)      | -                 | -                           |

|                   | RES ZERO- $\Omega$ JUMPER (use for STD config)    | -                 | -                           |

| R6                | RES 1.30kΩ 1%                                     | -                 | -                           |

| R7                | RES 243Ω 1%                                       | -                 | -                           |

| R8                | RES 120k $\Omega$ 1% (do not apply if VSBB < 20V) | -                 | -                           |

#### **Limitation of Warranties**

Information in this document is believed to be accurate and reliable. HOWEVER, THIS INFORMATION IS PROVIDED "AS IS" AND WITHOUT ANY WARRANTIES, EXPRESSED OR IMPLIED, AS TO THE ACCURACY OR COMPLETENESS OF SUCH INFORMATION. VICOR SHALL HAVE NO LIABILITY FOR THE CONSEQUENCES OF USE OF SUCH INFORMATION. IN NO EVENT SHALL VICOR BE LIABLE FOR ANY INDIRECT, INCIDENTAL, PUNITIVE, SPECIAL OR CONSEQUENTIAL DAMAGES (INCLUDING, WITHOUT LIMITATION, LOST PROFITS OR SAVINGS, BUSINESS INTERRUPTION, COSTS RELATED TO THE REMOVAL OR REPLACEMENT OF ANY PRODUCTS OR REWORK CHARGES).

Vicor reserves the right to make changes to information published in this document, at any time and without notice. You should verify that this document and information is current. This document supersedes and replaces all prior versions of this publication.

All guidance and content herein are for illustrative purposes only. Vicor makes no representation or warranty that the products and/or services described herein will be suitable for the specified use without further testing or modification. You are responsible for the design and operation of your applications and products using Vicor products, and Vicor accepts no liability for any assistance with applications or customer product design. It is your sole responsibility to determine whether the Vicor product is suitable and fit for your applications and products, and to implement adequate design, testing and operating safeguards for your planned application(s) and use(s).

VICOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED OR WARRANTED FOR USE IN LIFE SUPPORT, LIFE-CRITICAL OR SAFETY-CRITICAL SYSTEMS OR EQUIPMENT. VICOR PRODUCTS ARE NOT CERTIFIED TO MEET ISO 13485 FOR USE IN MEDICAL EQUIPMENT NOR ISO/TS16949 FOR USE IN AUTOMOTIVE APPLICATIONS OR OTHER SIMILAR MEDICAL AND AUTOMOTIVE STANDARDS. VICOR DISCLAIMS ANY AND ALL LIABILITY FOR INCLUSION AND/OR USE OF VICOR PRODUCTS IN SUCH EQUIPMENT OR APPLICATIONS AND THEREFORE SUCH INCLUSION AND/OR USE IS AT YOUR OWN RISK.

#### **Terms of Sale**

The purchase and sale of Vicor products is subject to the Vicor Corporation Terms and Conditions of Sale which are available at: (<u>http://www.vicorpower.com/termsconditionswarranty</u>)

#### **Export Control**

This document as well as the item(s) described herein may be subject to export control regulations. Export may require a prior authorization from U.S. export authorities.

Contact Us: http://www.vicorpower.com/contact-us

Vicor Corporation 25 Frontage Road Andover, MA, USA 01810 Tel: 800-735-6200 Fax: 978-475-6715 www.vicorpower.com

#### email

Customer Service: <u>custserv@vicorpower.com</u> Technical Support: <u>apps@vicorpower.com</u>

©2017 – 2019 Vicor Corporation. All rights reserved. The Vicor name is a registered trademark of Vicor Corporation. All other trademarks, product names, logos and brands are property of their respective owners.