边缘计算的重要性

更快的速度正变得无比重要。了解哪些应用正在蓬勃发展,以及为什么功率密度对未来的发展至关重要

严格的电压调节要求和极高的瞬态回转率意味着系统内的每一个电压降源和每一个功率耗损源,无论多么微小,都会产生可衡量的负面影响。因此,PCB 布局对于实现高性能电源至关重要。

作者:Joe Aguilar,高级经理,首席工程师

在这篇关于高性能 PCB 布局原理的概述中,Joe Aguilar 说明了散热设计方法并提供供电网络 (PDN) 概述,讲述降低阻抗的大电流路由策略以及设计高效去耦电容的一些重要考虑因素。

电源系统设计一般会关注从电源向负载供电所需的转换器、分立式组件和配件,不仅将印刷电路板 (PCB) 作为安装及路由层,而且还主要依靠反馈控制电路,弥补典型 PCB 中的大量小型损耗和阻抗。但近年来,用于人工智能和超级计算的处理器等高密度负载高级程度和速度都得到了提升,让每个组件的功能实现了最大化。

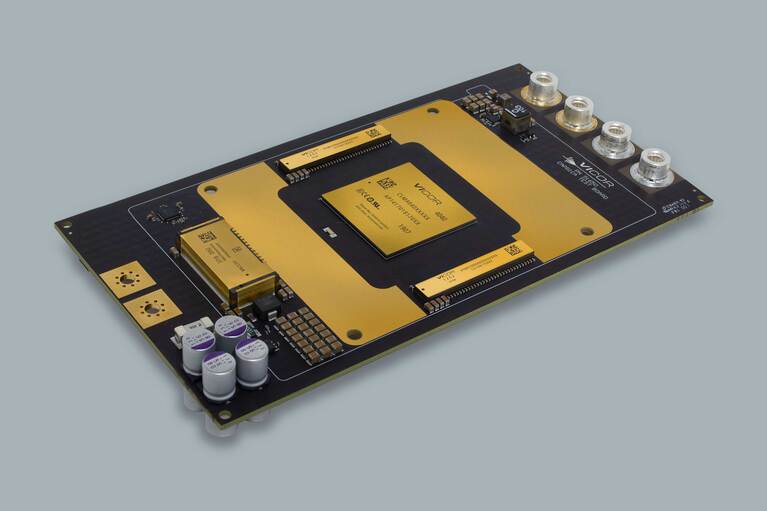

严格的稳压要求和极高的瞬态压摆率意味着:系统内压降的每个来源和功耗的每个来源,无论有多小,都会产生可测量的负面影响。因此,PCB 布局是实现高性能电源的关键。本文简要介绍高性能 PCB 布局的原理,其中包括散热设计方法、供电网络 (PDN) 概述、降低阻抗的大电流路由策略以及设计高效去耦电容的一些重要考虑因素。 图 1 是 Vicor 创建的最新设计的示例,主要针对测试和演示,将在本文中被使用。

图 1:在这个测试电路板中,一个 PRM™ 稳压器和两个 VTM™ 电流倍增器安装在一块高密度 PCB 上,为一个仿真高性能计算处理器的负载模块供电。工作时,将在 VTM 和负载模块上安装一款冷却板或散热器,另一款散热器将安装在 PRM 上。

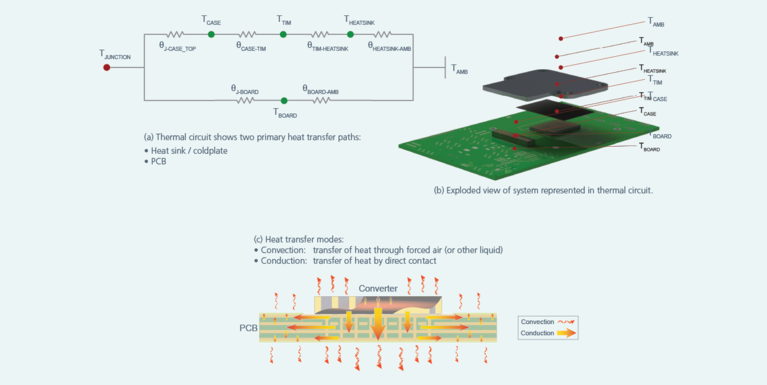

电力系统设计中的热管理目标是将热量从产热结点高效传递到周围空气中。一些传递会自然发生,但即使在常规设计中,一般也需要增加散热片和风扇。高密度系统需要在设计过程的早期对 PCB 进行详细的传热分析,以便最大限度将 PCB 本身作为热导体。

图 2:通过 PCB 的传导是高密度热管理的重要组成部分,需要使用等效电路来确定最有效的散热路径 (a)、(b)。良好的散热设计可优化传导和对流传热模式 (c)。

电力系统的主要热源是电源转换器等有源组件的内部结点。但对于拓扑散热模型而言,它们可以表示为等效电路一端的节点,见图 2(a)。来自该内部结点的热量,到达电源系统周围的环境空气中必须通过的每个组件或材料,可以表示为阻碍热量流向环境空气的阻抗器。一个等效热电路显示了最明显的路径热量源于一个电源转换器的内部结点:通过外壳、TIM,最后通过散热器进入周围空气。此外,它还显示了通过 PCB 的第二条不太明显的并行路径。第二条路径经常被忽视,但它对高密度电源设计的重要性再怎么强调也不为过。

热模型可能会变得相当复杂,因为每个网或位置的热阻抗都不同。无论复杂程度怎样,热模型都将识别出具有阻抗最低路径的网络,以将热量从组件的内部结点带走。设计人员随后可使用该信息最大限度增加导热,增加专门用于该网络的铜箔,即延长外部铜箔层,并使用热通孔增加超过最小表面积的表面积,以提高散热潜力。可适时使用各种类型的通孔:堆叠式通孔和埋孔、VIPPO 和传统经由通孔都是设计人员工具套件中的有效选项。

PDN 阻抗处于高密度计算电源系统的重要中心点区域,特别是 PCB 内的 PDN 阻抗。这些系统工作频率极高。在典型高性能计算电源系统中,PDN 由稳压器输出和传感点之间的几个组件组成,传感点通常位于 CPU 内部,要么在裸片上,要么在 BGA 互连上。旁路电容器、去耦电容器与相关通孔及 BGA 互连构成 PDN 的分立式组件。强大的超级计算处理器产生的高频率负载步进非常快,控制环路几乎无法将 PDN 的影响降至最低。这就是为什么 PDN 是设计中不可或缺的组成部分。

图 3:稳压器和 CPU 负载间供电网络 (PDN) 的分立式组件的阻抗会严重影响电源设计效果,特别是在高频率和大负载步进情况下。

预先定义 PCB 堆叠和平面图,这一点非常重要,其中包括总层数、专门用于电源和接地的层数以及所用铜箔的重量。接下来为路由信号连续接地层确定专用层。然后为需要阻抗控制路由、有寄生限制或将带来其它特殊注意事项的任何网络定义所需的层。在为流耗是 1000 安培以上的大电流处理器设计时,正确把握这一点至关重要。

一些估算方法将为早期阶段的 PCB 设计加速,使其更容易使用仿真来进一步完善设计。用平方法估算铜箔层电阻率是一种简单有效的方法。此外,平方法的一种变化方法也可用于估算相邻电源层和返回层的电感。

图 4:估算电源层电阻与电感的平方法。

此外,通孔电阻与电感也可通过简单的几何计算来估算,因为通孔可概念化为一个卷成筒的薄铜片。因此,通孔电阻 (R) 等于镀层电阻率 ((r) 与通孔长度 (L) 的乘积再除以镀层截面积 (A)。

图 5:通孔电阻可通过基于几何的简单经验法则估算。

寄生电容是 PCB 中阻抗的另一个重要来源,因此在任何仿真中都必须纳入。与电阻及电感的估算一样,近似计算 PCB 中的寄生电容从基本物理属性开始:一般来说,一对平行导体层之间的电容会随表面积的增大成正比增长;此外,其增长还与介电间距成反比。

图 6:PCB 中的寄生电容是两个层共享面积、这两层的间距和材料标称介电常数的函数。

数据来源:高速模拟设计与应用研讨会

高密度电源系统需要精挑细选的去耦电容器来过滤高频率开关噪声。这种应用需要电容器表现出极低的等效串联电阻 (ESR) 和适量的自谐振频率:超过该值,电容器将不再是有效的高频率噪声滤波器,因为由于等效串联电感 (ESL) 的原因,其阻抗会变为电感。总的来说,电容值甚至可能都不那么重要。

图 7:电容器的选择和通孔布置对于实现高频率开关噪声的低阻抗滤波至关重要。

实现低 ESR 和低 ESL 是首要目标,为此,设计人员应该考虑更小的低电感和反几何电容器,其不仅可将正负极更靠近一点,而且还可增加自谐振频率。周密布置组件和通孔,对于最小化环路电感非常重要。

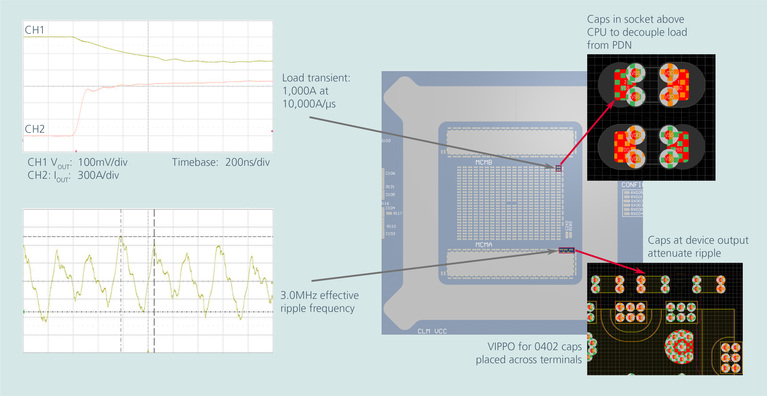

一个旨在用于以 10,000A/µs 的速率处理 1000A 负载步进的系统示例显示了极为靠近电源模块布置的 0402 去耦电容器如何衰减纹波以及插座中的其它电容器如何从 PDN 为负载去耦。

图 7:采用高性能通孔排列进行适当电容器选择和布置,可实现速率为 10,000A/µs 的 1000A 负载步进。

鉴于在当前高级处理器需要的电流量和电压精度方面电源要求的不断增加,因而为高性能计算和 AI 设计供电网络是一项非常复杂的挑战。因此,不仅需要散热和 PDN 设计的最新建模与估算技术,而且还需要先进的组件选择和安放标准。

如欲了解该主题的更深入讨论,请报名参加有关高性能 PCB 布局和散热设计技术的点播网络研讨会。

本文最初由 Signal Integrity Journal 发表。

Joseph Aguilar 是 Vicor DC-DC 产品应用高级经理。他作为应用工程师在电力电子行业拥有超过 15 年的经验。在 Aguilar 先生的职业生涯中,他从事的产品和应用范围很广,包括国防、工业、电信、照明和计算机。Aguilar 先生在他最近的工作中主要专注于高性能计算应用的产品和参考设计的开发。Aguilar 先生拥有马萨诸塞州斯普林菲尔德的西新英格兰学院的电子工程学士学位。

Joe Aguilar,高级经理,首席工程师

边缘计算的重要性

更快的速度正变得无比重要。了解哪些应用正在蓬勃发展,以及为什么功率密度对未来的发展至关重要

为未来提供动力: GenAI 供电创新

大型语言模型的功耗要求有多惊人?如何降低功耗?了解模块化电源的作用

随着人工智能(AI)的发展,电力挑战也随之而来

生成式人工智能(genAI)正在给软件、硬件和环境基础设施带来巨大压力。采用电源模块有助于实现更高的电流密度,从而将整体影响降至最低

微型数据中心引领边缘计算未来发展

HIRO 正在实现边缘计算的承诺。使用 Vicor 电源模块的医疗保健、教育和人工智能应用正在欧洲产生影响力